2007年12月20日 星期四

.

====== Ch5.7 Reduce Hit-Rate (四種) ======

※ (方法1) Small and Simple Caches :

1. A time-consuming portion of a cache hit is using the index portion of the address to read the tag memory and then compare it to the address. - smaller hardware is faster - keep the cache simple

2. main benefit of direct-mapped caches:the designer can overlap the tag check with the transition of the data.

※(方法2) Avoiding Address Translation During Indexing of the Cache :

1. Using virtual addresses for the cache, since hits are much more common than misses.

2. Why doesn’t everyone build virtually addressed caches ?

- One reason is protection

- another reason is that every time a process is switched the virtual addresses refer to different physical addresses, requiring the cache to be flushed.

※ (方法3) Pipelined Cache Access :

※ (方法4) Trace Caches :

- Instead of limiting the instructions in a static cache block to spatial locality, a trace cache finds a dynamic sequence of instructions including taken branches to load into a cache block.

- It comes from the cache blocks containing dynamic traces of the executed instructions as determined by the CPU transfer than containing static sequences of instructions as determined by memory.

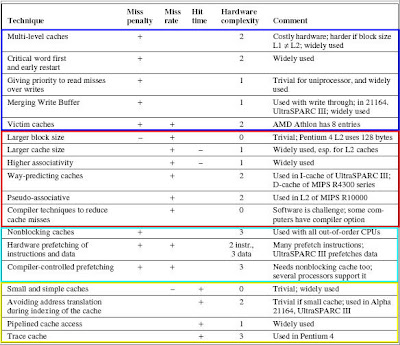

綜合分析: + 表示改進,– 表示負面影響。

Figure 5.26 ... from

Computer Architecture : A Quantitative Approach

1. A time-consuming portion of a cache hit is using the index portion of the address to read the tag memory and then compare it to the address. - smaller hardware is faster - keep the cache simple

2. main benefit of direct-mapped caches:the designer can overlap the tag check with the transition of the data.

※(方法2) Avoiding Address Translation During Indexing of the Cache :

1. Using virtual addresses for the cache, since hits are much more common than misses.

2. Why doesn’t everyone build virtually addressed caches ?

- One reason is protection

- another reason is that every time a process is switched the virtual addresses refer to different physical addresses, requiring the cache to be flushed.

※ (方法3) Pipelined Cache Access :

※ (方法4) Trace Caches :

- Instead of limiting the instructions in a static cache block to spatial locality, a trace cache finds a dynamic sequence of instructions including taken branches to load into a cache block.

- It comes from the cache blocks containing dynamic traces of the executed instructions as determined by the CPU transfer than containing static sequences of instructions as determined by memory.

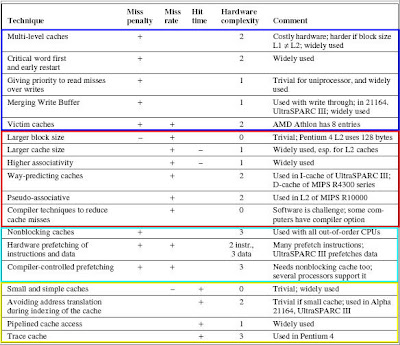

綜合分析: + 表示改進,– 表示負面影響。

Figure 5.26 ... from

Computer Architecture : A Quantitative Approach

全站熱搜

留言列表

留言列表