As we know, CPU includes 2 part.

One is CU (Control Unit), and the other is ALU (Arithmetics Logic Unit)

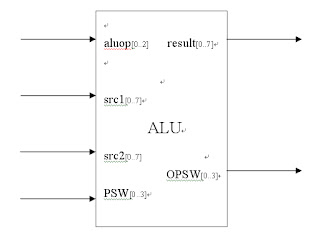

Let us design a 8-bit ALU by Belsa.

The ALU is as following :

-- ALU8.balsa : 8-bit ALU

----------------------------------------------------------

-- 2007.07.29 by 9679505 Amzshar Liu ( AaA )

----------------------------------------------------------

--

-- 4 input ( aluop, src1, src2, PSW )

-- 2 output ( result, OPSW )

--

-- aluop is 3 bits ALU Operation Code

--

-- aluop : AND, OR, XOR, RLC, RRC, ADDC, SUBC, NONE

-- aluop = 0b000 -> AND

-- aluop = 0b001 -> OR

-- aluop = 0b010 -> XOR

-- aluop = 0b011 -> RLC (Rotate Left 1 bit with Carry)

-- aluop = 0b100 -> RRC (Rotate Right 1 bit with Carry)

-- aluop = 0b101 -> ADDC (src1 + src2 + PSW.CY)

-- aluop = 0b110 -> SUBC (src1 - src2 - PSW.CY)

-- aluop = 0b111 -> NONE

--

-- src1, src2 is 8 bits

-- result is 8 bits ALU Result

--

-- PSW, OPSW is 4 bits (P, OV, AC, CY)

-- P is 1 bit Parity Flag

-- OV is 1 bit Overflow Flag (1:overflow)

-- AC is 1 bit Auxilary Carry Flag

-- CY is 1 bit Carry Flag

--

-- All Op must update "PSW.P" according to "result"

-- ADDC : Update PSW.CY, PSW.AC, OV

-- SUBC : Update PSW.CY, PSW.AC, PV

--

----------------------------------------------------------

type DataType is 8 bits -- src1, src2, result

P, OV, AC, CY : bit

end

aluop : OPType;

src1 : DataType;

src2 : DataType;

PSW : PswStatus

end

result : DataType;

OPSW : PswStatus

end

variable intmp : InputType

variable outtmp : OutputType

variable result : DataType -- outtmp.result

variable opsw : PswStatus -- outtmp.OPSW

-- variable P, OV, AC, CY : bit

variable src1tmp, src2tmp : DataType -- For ADDC, SUBC

variable CYtmp, Flag : bit -- For ADDC, SUBC

variable ADDSUB9 : 9 bits -- For ADDC, SUBC

shared add_sub is

begin

ADDSUB9 := ( src1tmp + src2tmp + CYtmp as 9 bits ) ;

result := ( #ADDSUB9[0..7] as DataType ) ;

---- Overflow Detection Logic : Overflow = CarryIn[N-1] XOR CarryOut[N-1]

opsw.OV := #ADDSUB9[8] xor #src1tmp[7] xor #src2tmp[7] xor #ADDSUB9[7] ;

if( Flag = 0 ) then

opsw.AC :=( ( (not #src1tmp[4]) and (not #src2tmp[4]) and #result[4] ) or

( (not #src1tmp[4]) and #src2tmp[4] and (not #result[4]) ) or

( #src1tmp[4] and (not #src2tmp[4]) and (not #result[4]) ) or

( #src1tmp[4] and #src2tmp[4] and #result[4] ) ) ;

opsw.CY := #ADDSUB9[8]

---- Because src2tmp = 1's complement of intmp.src2

opsw.AC :=( ( (not #src1tmp[4]) and (not #src2tmp[4]) and (not #result[4]) ) or

( (not #src1tmp[4]) and #src2tmp[4] and #result[4] ) or

( #src1tmp[4] and (not #src2tmp[4]) and #result[4] ) or

( #src1tmp[4] and #src2tmp[4] and (not #result[4]) ) ) ;

opsw.CY := not #ADDSUB9[8]

end -- end begin

shared ParityCheck is

begin

opsw.P := #result[0] xor #result[1] xor #result[2] xor #result[3] xor

#result[4] xor #result[5] xor #result[6] xor #result[7]

end -- end begin

begin

loop

in_sigs -> intmp ;

-- P := intmp.PSW.P

-- OV := intmp.PSW.OV

-- AC := intmp.PSW.AC

-- CY := intmp.PSW.CY ;

opsw := intmp.PSW ;

intmp.PSW.AC, intmp.PSW.CY ;

0b000 then ---- AND

result := intmp.src1 and intmp.src2 ;

print "aluop=000 : ", #intmp.src1, " AND ", #intmp.src2, " => ", #result

0b001 then ---- OR

result := intmp.src1 or intmp.src2 ;

print "aluop=001 : ", #intmp.src1, " OR ", #intmp.src2, " => ", #result

0b010 then ---- XOR

result := intmp.src1 xor intmp.src2 ;

print "aluop=010 : ", #intmp.src1, " XOR ", #intmp.src2, " => ", #result

0b011 then ---- RLC : (Rotate Left 1 bit with Cary)

result := ( #intmp.PSW.CY @ #intmp.src1[0..6] as DataType ) ;

opsw.CY := #intmp.src1[7] ;

print "aluop=011 : ", #intmp.src1, " RLC => ", #result

0b100 then ---- RRC : (Rotate right 1 bit with Cary)

result := ( #intmp.src1[1..7] @ #intmp.PSW.CY as DataType) ;

opsw.CY := #intmp.src1[0] ;

print "aluop=100 : ", #intmp.src1, " RRC => ", #result

0b101 then ---- ADDC is " result := src1 + src2 + CY " and Updated PSW

---- => result := src1tmp + src2tmp + CYtmp

src1tmp := intmp.src1 ;

src2tmp := intmp.src2 ;

CYtmp := intmp.PSW.CY ;

Flag := 0 ;

add_sub() ;

print "aluop=101 : ", #intmp.src1, " ADDC ", #intmp.src2, " => ", #result

0b110 then ---- SUBC is " result := src1 - src2 - CY " and Updated PSW

---- => result := src1 + ( (not src2) + 1 ) - CY

---- => result := src1 + ( not src2) + ( 1 - CY )

---- => result := src1tmp + src2tmp + CYtmp

src1tmp := intmp.src1 ;

---- Here for src2 1's complement

src2tmp := ( not intmp.src2 + 1 as DataType ) ;

---- Here (+1 - CY) for src2 2's complement

CYtmp := ( not intmp.PSW.CY as bit ) ;

Flag := 1 ;

add_sub() ;

print "aluop=110 : ", #intmp.src1, " SUBC ", #intmp.src2, " => ", #result

0b111 then ---- NONE

print "alop=111 : NONE ! " ;

continue

end; -- end case intmp.aluop

ParityCheck();

out_sigs <- outtmp ;

print ">>>=====================================================>>>"

end -- end loop

end -- end begin

- 5月 12 週一 200822:22

[EE_CSIE] 非同步電路設計Lab2. Aync 8 bit ALU

- 5月 12 週一 200822:21

[EE_CSIE] 非同步電路設計Lab1 - Wagging Shift Register

這是我們 非同步電路設計 Project / LAB1 ,用 Balsa 語言寫一個 Wagging Shift Register procedure srd1(input i : byte ; output o1 : byte ; output o2 : byte) is procedure sre1(input i1 : byte ; input i2 : byte ; output o : byte) is procedure srw8a(input i : byte ; output o : byte) is procedure srw8c(input i : byte ; output o : byte) is

-- 20070515 by 9679505 / Amzshar Liu ( AaA )

import [balsa.types.basic]

variable x : byte

begin

loop

i -> x ; -- Input Communication

o <- x -- Output Communication

end -- end loop

end

i -> [x -> y] -> o

--)

variable x, y :byte

channel cl : byte

begin

loop

o <- y

i -> x ;

y := x

end -- end loop

end

========================================

-- SRD1.balsa : demux i to o1, o2 alternately

--- 20070515 by 9679505 / Amzshar Liu ( AaA )

import [balsa.types.basic]

variable x, y : byte

begin

loop

-- read channel i into register x while writing register y to channel o2

i -> x o2 <- y ;

-- read channel i into register y while writing register x to channel o1

i -> y o1 <- x

end -- end loop

end

========================================

-- SRE1.balsa : demux i1, i2 into o alternately

-- 20070515 by 9679505 / Amzshar Liu ( AaA )

import [balsa.types.basic]

variable x, y : byte

begin

loop

i1 -> x o <- y ;

i2 -> y o <- x

end -- end loop

end

========================================

-- SRW8A.balsa: Multi-Stage Wagging Shift Register

-- 20070515 by 9679505 / Amzshar Liu ( AaA )

import [balsa.types.basic]

import [SRA1]

import [SRD1]

import [SRE1]

constant n = 8

array 1..n/2 of channel c1, c2 : byte

begin

srd1(i, c1[1], c2[1])

sre1(c1[n/2], c2[n/2], o)

for i in 1..(n/2)-1 then

sra1(c1[i], c1[i+1])

sra1(c2[i], c2[i+1])

end -- end for

end

========================================

-- SRW8C.balsa: Multi-Stage Wagging Shift Register

-- 20070515 by 9679505 / Amzshar Liu ( AaA )

import [balsa.types.basic]

import [SRC1]

import [SRD1]

import [SRE1]

constant n = 8

array 1..n/2 of channel c1, c2 : byte

begin

srd1(i, c1[1], c2[1])

sre1(c1[n/2], c2[n/2], o)

for i in 1..(n/2)-1 then

src1(c1[i], c1[i+1])

src1(c2[i], c2[i+1])

end -- end for

end

========================================

- 5月 12 週一 200822:19

[EE_CSIE] 交大電資所 暑修

想說可以在開學前抵9學分,於是想要來暑修一下

(唉!要是以前大學那麼用功就好了~ >"< )

這次交大資工所"暑假"共開了四門課,

-------------------------------

課號 課程名稱 學分 開課系所 開課教師

5017 視訊壓縮 3.00 電機專 蕭旭峰

5018 資料探勘 3.00 電機專 彭文志/黃俊龍

5019 計算機運算,組織與分類 3.00 電機專 鍾崇斌

5020 非同步電路設計 3.00 電機專 陳昌居

-------------------------------

上週三(7/4) 去聽了彭教授的Data Mining(資料探勘),覺得這是一門非常有趣的課,但是覺得兩個月內要修完,可能無法學到爐火純青的境界,所以等正課的時候再來修好了。是門需要 Databse、Statistics and Algorithm 技巧的課程。

課程綱要:

1. Introduction to data mining

2. Mining association rules

3. Data classification

4. Data warehouse and OLAP

5. Data clustering

6. Mining sequential patterns

7. mining

8. Stream data mining

9. Sensor data mining

10.Privacy data mining

... ... ... more ... ... ...

-------------------------------

上週六(7/7)早上 9:00~16:30 則是去聽鍾教授的"計算機運算,組織與分類",聽說是第一次開這樣的課程。因為對姓鍾感到特別親切,而且以前也修過鍾教授的"嵌入式系統",所以週末還是頂著大太陽去聽課。

嗯,聽了之後覺得可以複習大二到大四的計算機組織、機算機結構、數位邏輯...是門非常有廣度的課呦。

Summary :

1. Digital electronics—Semiconductor, devices, IC, and MOS electronics

2. Digitalization and digital systems

3. Combinational circuits—Fundamentals, simplification, design, and array logic

4. Sequential circuits—Fundamentals, analysis, simplification, and design

5. Computer abstractions and technology

6. Instructions: Language of the computer

7. Arithmetic for computers

8. Assessing and understanding performance

9. The processor: Datapath and control

10.Enhancing performance with pipelining

11.Computer categorization

-------------------------------

上週四(7/5)則是聽了陳教授的 Asyncronous Circuit Design,是一種不用 Clock 的電路設計,這真

是太酷了,有以下優點:Low power consumption, High operating speed, Less emission of electro-magnetic noise, Robustness towards variations in voltage, temperature,

and fabrication process parameters, Better composability and modularity,

and No clock distribution and clock skew problems。

最後,幾經考慮,決定修這個, ㄏㄏ ... (因為每個都想修 ... Orz ...

-------------------------------

.End.