.

====== Ch5.8 Main memory and Organization for improving performance (三種) ======

※ 1. Wider Main Memory : 若寬度變兩倍,存取記憶體只需原來的一半

※ 2. Simple Interleaved Memory : 簡單交錯式的記憶體

※ 3. Independent Memory Banks : 獨立式記憶體庫

====== Ch5.10 Virtual Memory ======

※ Virtual Memory (虛擬記憶體) :

1. A means of sharing a smaller amount of physical memory among many processes.

2. It divides physical memory into blocks and allocates them to different processes.

※ There are further differences between caches and virtual memory beyond those quantitative :

1. Replacement on cache misses is primarily controlled by hardware, while virtual memory replacement is primarily controlled by the operating system. The longer miss penalty means it’s more important to make a good decision, so the operating system can be involved and spend take time deciding what to replace.

2. The size of the processor address determines the size of virtual memory, but the cache size is independent of the processor address size.

3. In addition to acting as the lower-level backing store for main memory in the hierarchy, secondary storage is also used for the file system. In fact, the file system occupies most of secondary storage. It is not normally in the address space.

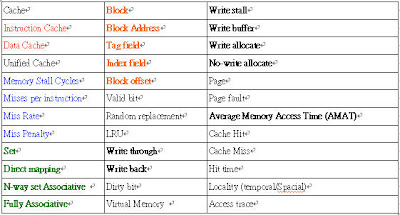

※ Translation lookaside buffer (TLB) 轉換後備緩衝區 :

- also called translation buffer (TB)

- It is special address translation cache.

- A TLB entry is like a chche entry where the tag holds portions of the virtual address and the data portion hold a physical page frame number, protection field, valid bit, and usually a use bit and dirty bit.

※ Selecting a Page Size : 分頁大小

=> The following favor a larger size:

1. The size of the page table is inversely proportional to the page size; memory (or other resources used for the memory map) can therefore be saved by making the pages bigger.

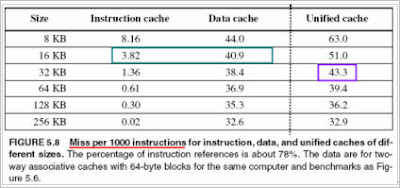

2. As mentioned on page 433 in section 5.7, a larger page size can allow larger caches with fast cache hit times.

3. Transferring larger pages to or from secondary storage, possibly over a network, is more efficient than transferring smaller pages.

4. The number of TLB entries are restricted, so a larger page size means that more memory can be mapped efficiently, thereby reducing the number of TLB misses.

====== Ch5.11 Protection and Examples of Virtual Memory ======

※Protecting Processes

The simplest protection mechanism is a pair of registers that checks every address to be sure that it falls between the two limits, traditionally called base and bound. An address is valid if

Base <= Address <= Bound

In some systems, the address is considered an unsigned number that is always added to the base, so the limit test is just

(Base + Address) <= Bound

※ the Computer Designer has 3 more responsibilities in helping the OS Designer protect processes from each other:

1. Provide at least two modes, indicating whether the running process is a user process or an operating system process. This latter process is sometimes called a kernel process, a supervisor process, or an executive process.

2. Provide a portion of the CPU state that a user process can use but not write. This state includes the base/bound registers, a user/supervisor mode bit(s), and the exception enable/disable bit. Users are prevented from writing this state because the operating system cannot control user processes if users can change the address range checks, give themselves supervisor privileges, or disable exceptions.

3. Provide mechanisms whereby the CPU can go from user mode to supervisor mode and vice versa. The first direction is typically accomplished by a system call, implemented as a special instruction that transfers control to a dedicated location in supervisor code space. The PC is saved from the point of the system call, and the CPU is placed in supervisor mode. The return to user mode is like a subroutine return that restores the previous user/supervisor mode.

End.